有别于上一代Netburst,Intel Core微架构将会统一用于桌面电脑(Conroe)、笔记本电脑(Merom)及主流服务器(WoodCrest)产品中。据Intel表示Core微架构整合了Mobile架构的省电高效率与Netburst优秀功能,并为Multi-Core应用作出准备及优化。话虽如此但我们却很难在Core微架构中找到半点Netburst的影子,而且它的设计近乎90%是基于Mobile架构的Yonah核心作出改良,而只保留了NetBurst架构中的Prefetching,因此把Core微架构说成把Netburst和Mobile架构结合是有点牵强。

虽然Intel Core微架构是基于Yonah的设计,但其实约有70-80%的架构和电路被重新设计,并加入了五大重要创新,其中包括Intel Wide Dynamic、Intel Intelligent Power Capability、Intel Adcanced Smart Cache、Intel Smart Memoru Acess及Intel Adcanced Digital Media Boost,下面就让我们来对这五大重要创新进行一个介绍。

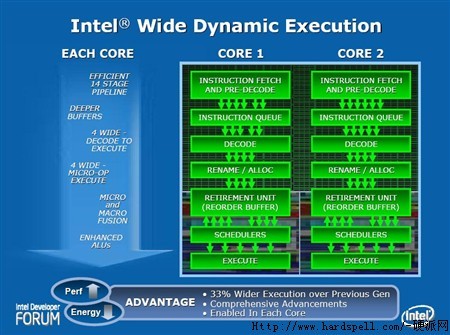

五大创新之Intel Wide Dynamic Execution

由Pentium Pro开始,Intel加入了Dynamic execution动态执行,让x86处理器首次支持Data Flow Analysis、Speculative Execution、Out of Order Execution及Super Scalar等RISC的处理器技术技术。直至Pentium 4的NetBurst架构则被再度改良称为Advanced Dynamic Executive,它采用更深的Out of Order Speculative Executive引擎,以让高Pipeline Stage(管线等级)架构减少浪费,同时改善Branch-Prediction机制来减少造成分支预测错误,避免性能过于低下。

明显地Intel Core微架构的Wide Dynmaic Execution和Adcanced Dynamic Executive意义不同,它的出发点在于如何提高每周期指令处理数目,改善执行时间及提升处理器的功耗表现,Core微架构拥有4组Decoder(3 Simple decoders + 1 Complex decoder),比上代Pentium Pro(P6)/PentiumII/PentiumIII/Pentium M架构拥有2 Simple decoders + 1 Complex decoder可多处理一组指令,与AMD K8不同的是它只拥有3组Complex ecoders,正常来说大部份x86指令均可以采用Simple Coder把它翻译成一个Micro-Op指令,只有极少数学运算的指令,需要采用Complex decoders来把它翻译为四个Micro-Ops指令,因此在正常情况下Core微架构对比Netburst及K8有更优秀的指令执行效率。取消了高频率政策,Intel Core微架构用回较高效率的14层管线,为了提升分支预测的性能及准确性,Branch Predictor的Bandwitdh提升20B(K8、Banias为16B,Netburst为4B),这就是所谓的Wide。

Wide Dynamaic Execution首次加入了Macro-Fusion技术。在上一代的微架构中,每个指令被送来时其解码及执行操作是完全独立的,但Intel Core微架构可以让常见的指令组例如一个Compare指令配随后拥有一个Jump指令,便可把这个指令组合成单一的Micro-Op指令,这让Core微架构在特定情况下每个周期可运算五组指令,据Intel表示大部份x86程序,约每十至十五个指令就会出现一组可通过Macro -Fusion被组合,因此减少了程序执行所需运算时间、提升性能却不会增加处理器的功耗,为此Intel也改进了ALU(Arithmetic Logic Unit)部份以支持Macro-Fusion技术。

此外Intel Core微架构保留了Banias微架构的Micro-op Fusion技术,在现代的x86处理器,x86指令(Macro-ops)会被分拆去为长短相同的Micro-Ops指令,才会被送往处理器的Pipeline等待执行,而Micro-op Fusion能把相同的Macro-ops混合成单一个Micro-ops,减少了Micro-ops运算的数目也让处理器运行流程更有效率,据Intel表示Micro-op Fision通过Out-of-order逻辑可以减高达10%的Micro-op指令执行数。总括而言Macro-Fusion及Micro-op Fision提升了核心的执行效率同时保持了低功耗。

- 第1页:扬眉吐气!新一代PC性能换代至酷至睿

- 第2页:Netburst下马!酷睿2危急处力拨狂澜

- 第3页:五大重要创新!Intel Core微架构解析(1)

- 第4页:让处理器更Smart!Intel Core架构解析(2)

- 第5页:没内存控制器照样强,Core微架构解析(3)

- 第6页:更强更智能!Intel Core微架构解析(4)

- 第7页:界线模糊化!Intel新一代处理器命名解析

- 第8页:Core 2 Duo/Core 2 Extreme价格/规格剖析

- 第9页:AMD性能没了优势,724让价格更公道、实在

- 第10页:好马配好鞍——Intel发布全新系列芯片组支持Core

- 第11页:好马配好鞍——主流取向:全新96x芯片组介绍(1)

- 第12页:好马配好鞍——主流取向:全新96x芯片组介绍(2)

- 第13页:好马配好鞍——低端取向:全新946系列芯片组介绍

- 第14页:扣肉虽香,Conroe与芯片兼容性问题非常关键

- 第15页:狂超破2.8GHz!E6300/E6400超频潜力巨大

- 第16页:Intel Core 2 Extreme X6800领跑未来新纪录

- 第17页:测试平台与说明

- 第18页:性能测试——整机性能:SYSMARK 2004

- 第19页:性能测试——综合性能:WorldBench 5

- 第20页:性能测试——商业性能:Winstone 2004

- 第21页:性能测试——专业3D渲染性能:Cinbench 9.5/3Dsmax 7.0

- 第22页:性能测试——音/视频压缩性能:DivX/WME9/H.264/iTunes

- 第23页:性能测试——游戏性能:HL 2/Quake 4/Battlefield2

- 第24页:性能测试——游戏性能:Ris Of Legends/F.E.A.R.

- 第25页:性能测试——缓存性能:4MB VS 2MB二级缓存

- 第26页:性能测试——FSB 性能:1333MHz VS 1066MHz前端总线

- 第27页:江山易主!新一代的性能王者诞生

硬评:一分钟了解i5-9400F性能

硬评:一分钟了解i5-9400F性能 7nm锐龙直击 AMD发布会图赏

7nm锐龙直击 AMD发布会图赏