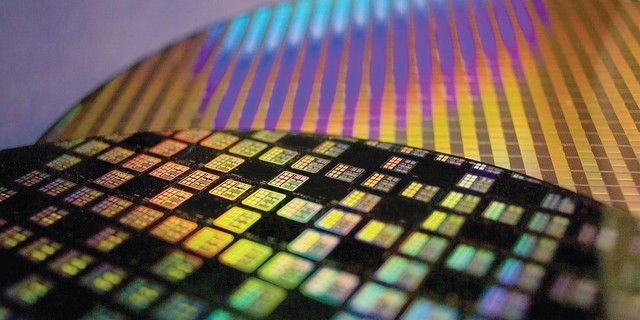

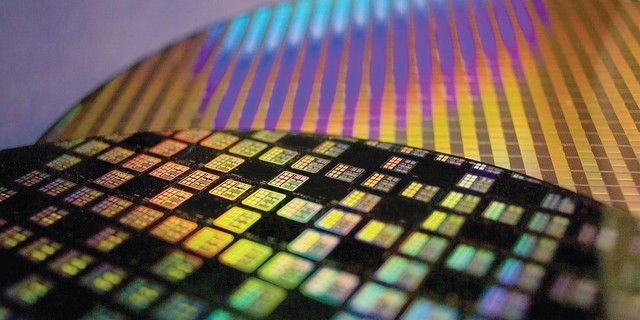

据外媒报道,台积电宣布它们已经5纳米工艺的基础设计,将进一步提升晶体管的密度和性能,这次的5纳米工艺是台积电第二次使用EUV极紫外光刻机技术,从而提高产量和性能,上一次使用EUV技术是7nm的时候。

台积电5nm基础设计完成 已开始风险生产(图片来自techpowerup)

据悉,台积电对5nm很有信心,因为对比7nm提升很大,它们使用了Arm Cortex-A72内核举例,逻辑密度提高1.8倍,时钟速度增加15%,每个晶圆的芯片数量将更多。这个工艺适用于移动,互联网和高性能计算应用程序。

除了5nm工艺,台积电还为硅设计流程方案提供在线工具,这些方案对5nm工艺进行了优化,据说台积电现已开始风险生产。

点评:台积电5nm工艺提升性能具体我们不得而知,不过可以明确的是5nm到来不远了,摩尔定律发展到今天,制程工艺进步越来越困难,就现在的情况看,5nm将会停留很久时间。

本文属于原创文章,如若转载,请注明来源:台积电5nm基础设计完成 对比7nm提升很大//cpu.zol.com.cn/713/7137002.html